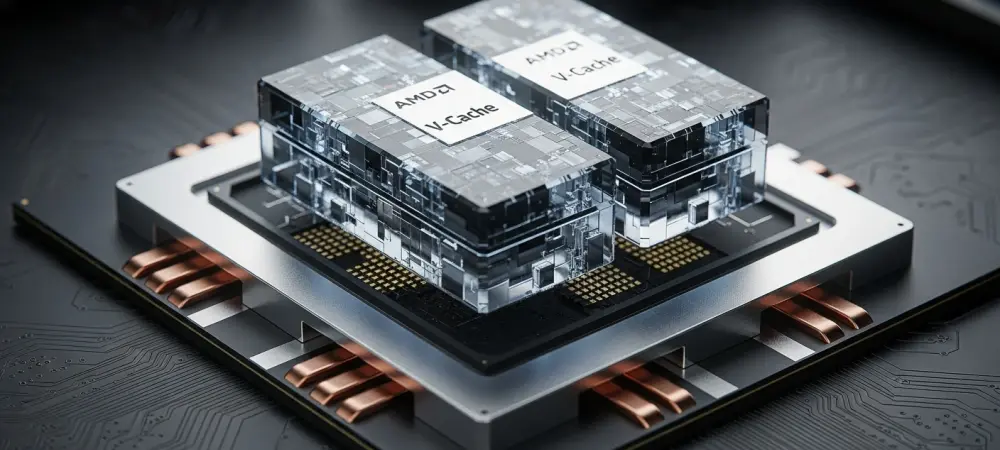

The long-standing wall between high-frequency professional workstations and memory-intensive gaming machines has finally crumbled under the weight of sheer silicon innovation. For years, the hardware industry operated on a binary logic: if a user wanted the highest frame rates, they sacrificed clock speeds for cache; if they wanted heavy multi-threaded productivity, they bypassed specialized gaming chips. The Ryzen 9 9950X3D2 “Dual Edition” dismantles this boundary by being the first consumer processor to integrate 3D V-Cache on both of its compute dies. With a staggering 208 MB of total cache, the silicon moves beyond the realm of simple gaming upgrades to become a foundational shift in how desktop processors manage massive, complex datasets.

This 16-core, 32-thread CPU marks a definitive moment where hardware compromise is no longer a prerequisite for performance. By doubling the cache capacity across the entire chip rather than limiting it to a single cluster, AMD has addressed the “scheduling tax” that previously hindered multi-CCD gaming chips. This architecture ensures that data-heavy instructions stay on-chip, reducing the need to communicate with slower system RAM. Consequently, the processor serves as a specialized tool for those who refused to choose between the raw compute power needed for compilation and the latency sensitivity required for elite-level simulation.

The 208 MB Milestone: The End of Hardware Compromise

The arrival of a 208 MB total cache pool signals a new era in which the traditional bottleneck of memory latency is bypassed through sheer volume. In previous generations, users were forced to choose a specific die for specific tasks, often leading to uneven performance in hybrid workloads. The Dual Edition configuration eliminates this imbalance, providing a symmetrical environment where every core has direct, high-speed access to a massive reservoir of L3 cache. This transition is not just about incremental gains; it is about changing the fundamental physics of data retrieval within the desktop environment.

By moving beyond the limitations of single-die cache stacking, this processor effectively functions as a bridge to the next decade of software development. As applications in AI and real-time data processing become more common on the desktop, the ability to store enormous data sets directly on the processor becomes a critical advantage. This release effectively ends the era of specialized “gaming only” chips, as the massive cache now provides tangible benefits across the entire spectrum of high-end computing tasks.

Bridging the Gap: Enthusiast Gaming and Professional Workflows

Historical limitations of 3D V-Cache often involved thermal bottlenecks and significant clock speed penalties, which turned many professional users away from these specialized parts. To combat this, a radical shift in packaging was implemented. By placing the SRAM tiles beneath the compute dies rather than on top of them, the thermal transfer between the cores and the integrated heat spreader is significantly improved. This architectural evolution allowed the 16-core powerhouse to maintain a 5.6 GHz boost clock, a feat previously thought impossible for a dual-cache arrangement.

This technical breakthrough signals a transition where server-grade memory bandwidth is no longer exclusive to data centers. Creators and developers who demand peak performance can now access the same type of technology used in high-performance computing clusters. The ability to maintain high frequencies while providing massive cache volumes means that tasks like video editing and 3D rendering no longer feel like a step down from dedicated productivity chips. Instead, the hardware provides a seamless experience that scales according to the complexity of the professional workflow.

Under the Hood: Dual-Cache Architecture and Performance Trade-offs

The technical centerpiece of the 9950X3D2 is its symmetrical design, featuring 64 MB of 3D V-Cache on each of its two compute dies (CCDs) for a total L3 pool of 192 MB. While this configuration provides a “no compromises” approach, it comes with specific operational costs that the enthusiast market must consider. The most notable is the 200W Thermal Design Power (TDP), which requires high-end cooling solutions. Additionally, there is a slight 100 MHz reduction in boost clock compared to its single-cache predecessor, a necessary sacrifice to ensure stability across both cache-heavy dies.

To maintain efficiency, the chip utilizes advanced core-parking functionality to manage cross-die communication. This logic ensures that latency-sensitive tasks are prioritized on the most efficient pathways, while the massive cache serves data-heavy operations. Managing two cache pools requires sophisticated software interaction, making the chip dependent on the latest chipset drivers to function correctly. This complexity is the price of admission for a processor that attempts to do everything at an elite level, balancing power consumption with unprecedented memory access speeds.

Benchmarking Production Gains: Analyzing the Market Rivalry

Early analysis indicated that the dual-cache configuration provided a tangible performance uplift in production environments, offering a 5% to 13% boost in tasks like 3D rendering and AI data science. These workloads thrived on the increased on-chip memory, which allowed complex calculations to stay resident on the CPU for longer periods. This release highlighted a widening strategic divide in the industry: while Intel pivoted toward a value-driven approach with its Core Ultra 200S Plus series to capture the mass market, AMD doubled down on the premium “silicon lottery” segment.

The 9950X3D2 was clearly positioned as a niche powerhouse, catering to those who required extreme memory bandwidth and were willing to pay the highest consumer price bracket. This rivalry defined the landscape, as users weighed the benefits of AMD’s massive cache against Intel’s focus on core density and price-to-performance ratios. The competition drove innovation to new heights, forcing both companies to reconsider how they balanced architectural complexity with consumer demand for reliable, high-speed computing.

Preparing the Desktop: The April 22 Launch and Beyond

Potential owners considered the architectural shifts necessary to accommodate such a high-power component. Cooling manufacturers adjusted their strategies to meet the 200W thermal requirements, while software developers updated scheduling algorithms to prioritize the massive cache pools. As the April 22 release date approached, users evaluated whether their specific workloads, particularly those involving large-scale data sets or complex compilation, aligned with the unique bandwidth advantages provided by this massive dual-cache architecture.

The industry viewed this release as a bellwether for future desktop designs. Systems integrators prepared for the launch by validating power delivery modules on high-end motherboards, ensuring that the 9950X3D2 operated within its intended performance envelope. This evolution suggested that the focus of high-end computing shifted from raw frequency toward specialized memory density. The debut of this processor established a new benchmark for what a flagship desktop component achieved, influencing how professionals and enthusiasts alike approached their hardware investments for the coming years.